project manager 를 누르고 source 를 눌러서 design sources 안에 add2를 눌러 다시 들어갈수 있습니다.

또는

and2를or2로 바꿔보겠습니다.

assign y = a| b;

상태로 source를 다시 실행해보겠습니다.

여전히 and 상태인것을 확인할 수 있습니다.

xilinx에서 vivado tool 은 시뮬레이션과 회로합성과정이 따로여서

simulation 툴을 열면 열때의 source 코드로 계속 simulation 한다

simulation 을 나갓다가 다시 들어오던가 위에 있는

relaunch simulation을 눌러서 스스로 빠져나갔다가 다시 들어옴

다시 run 을 눌러서 실행 시킵니다.

or가 되어있는 상태를 확인하였습니다.

다시 and로 고치고 저장해서 오른쪽 버튼

save file as 해서 xor2.v로 저장할때 해야할것들은

- module 이름 변경

- assign y = a ^ b;

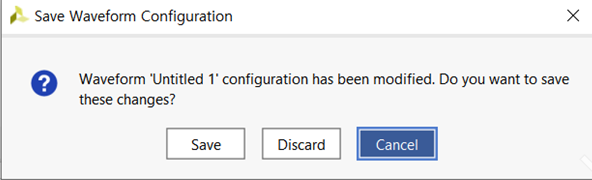

위의 untitled1은저장하지 않는다.

만약 저장을 하게 된다면 wave form configration파일로 저장이 되는데

그러면 나중에 지우는게 좋다.

xor2.v는 저장되었는지 확인한다.

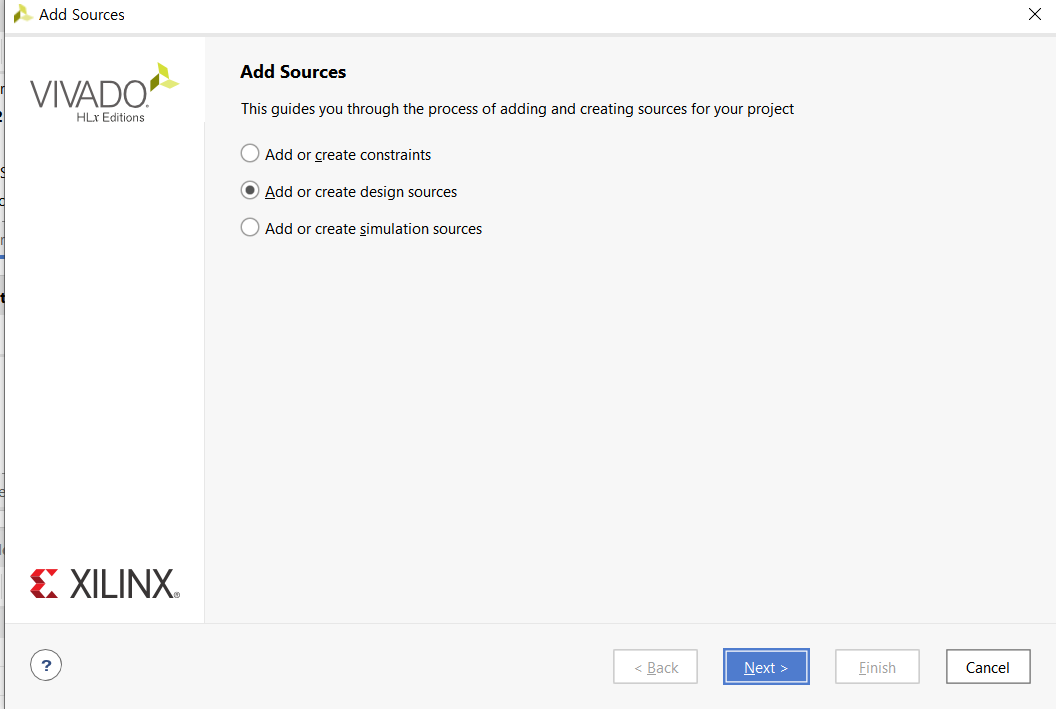

이제 왼쪽의 source창에 source들을 추가해줘야하는데

그럴려면 옆에 add source(ALT + A)를 눌러서

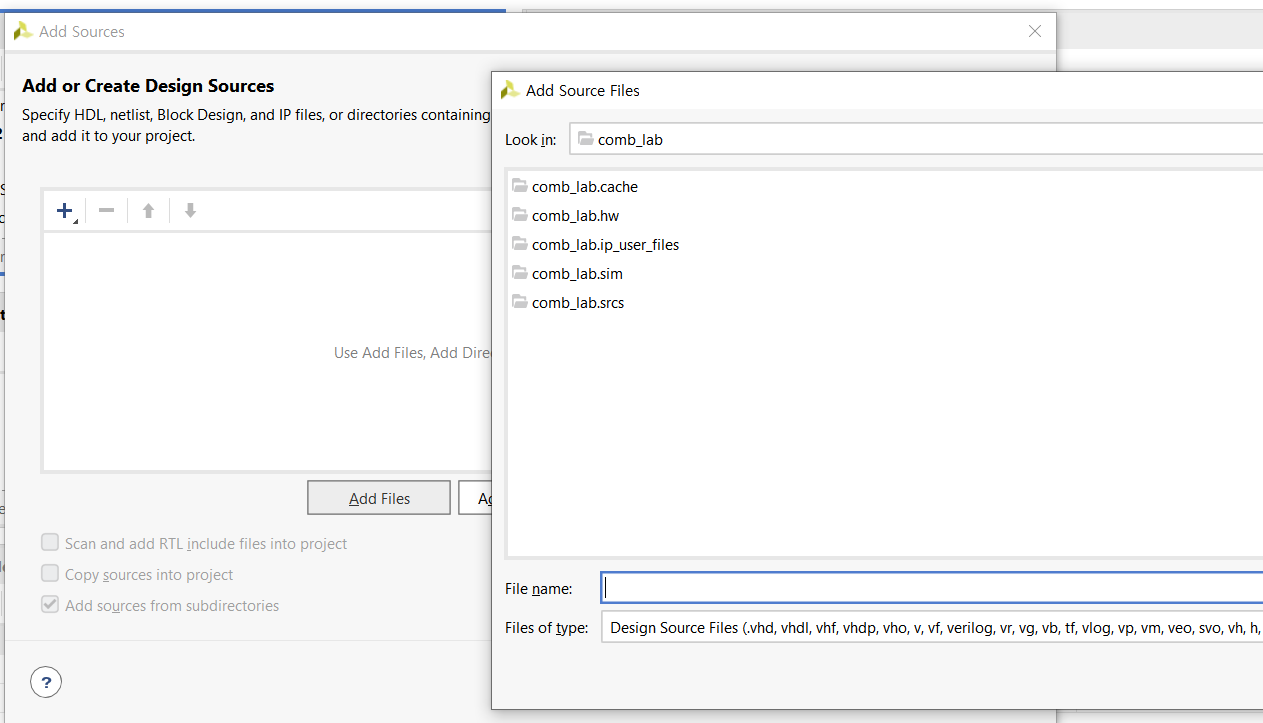

add file 해서 만든 xor.v파일을 추가해준다.

add files

오른쪽에 recent directories에서 예전 파일 찾기

finish

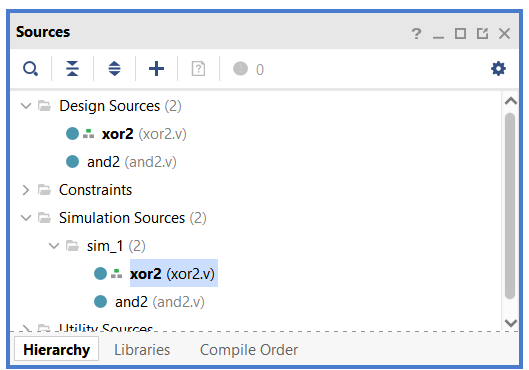

굵게 표현되어있는게 내가 현재 진행하는 파일이다.

top design을 바꿔줘야한다.

오른쪽 버튼 set as top을 누르면 xor2가 현재 메인 파일이 됩니다.

simulation을 위한 top design과 design source의 top desgin이 다를수 있다.

여기서 xor을 set as top을 눌러 top design으로 해줍니다.

run simulation 을 해줍니다.

(아직 simulation을 안지웠다면 ) simulation 밑에 wave forn을 눌러서 delete 를 눌러준다.

시뮬레이션을 하려고 했더니 이런 오류가 뜬다.

boost::filesystem::remove: 다른 프로세스가 파일을 사용 중이기 때문에 프로세스가 액세스 할 수 없습니다:

"D:/FPGA/comb_lab/comb_lab.sim/sim_1/behav/xsim/simulate.log"

해결하려면 우선다시 껐다 켜보자.

만약 옆에 simulation에 a b y가 안뜬다면

(simulation) a shift 맨밑 -> 전체선택

add to wave window

위에서 만들어놓은 tcl 파일을 열어야한다.

file 밑에 file 표시를 눌러서 open file을 눌러서 저장해놓은 위치의 tcl 파일을 불러온다.

error no search HDL direct / and2 라는 에러가 뜬다.

그럴때

add force _ 여기 중간것 모두 지움_ a {0 0ns} {1 50 ns} ......

add_force a {0 0ns} {1 50ns} -repeat_every 100ns

add_force b {0 0ns} {1 25ns} -repeat_every 50ns

이렇게 적어서 simulation 으로 돌아가서

다시 source를 돌리면

simulation 이 돌아간다.