vivado second project gate2.v 제작(1)

목차

1. gate2.v file을 생성하기 위해 and2.v 를 copy

해서 사용해보겠습니다.

2. gate2.v에 대한 simulation을

(1) GUI를 통한 반복 신호 설정

(2) tcl file을 활용한 simulation

3. gate2.v에 대한 회로도 확인

(1) RTL회로도

(2) Synthesis 결과 회로도

를 확인해보겠습니다.

어제 생성한 comb_lab파일을 열어서 작성해보겠습니다.

gate2.v file을 생성하기 위해 and2.v 를 copy해서 사용해보겠습니다.

save as로 저장해서 gate2.v파일을 만들어주세요.

이렇게 하는 이유는 comb_lab안에 파일을 전부 넣기 위해서입니다.

Bitwise Operator들을 적용한 조합회로에 대한 회로설계를 하겠습니다.

파일이름을 gate2로 설정하겠습니다.

gate2 에 대한 Verilog HDL code를 작성하겠습니다.

module gate2(

input a, b,

output y_not, y_and, y_or, y_xor, y_nand, y_nor, y_xnor

);

assign y_not = ~a;

assign y_and = a & b;

assign y_or = a | b;

assign y_xor = a ^ b;

assign y_nand =~(a & b);

assign y_nor = ~(a | b);

assign y_xnor = ~(a ^ b);

endmodule

작성한 gate2.v를 source에 올려주세요

gate2.v를 눌러서 오른쪽 버튼 set as top을 눌러서 제일 위로 올려주세요

shematic을 확인해보겠습니다.

simulation을 해보겠습니다.

어제 만든 and2.tcl 파일을 불러와서 열어보겠습니다.

file + open file을 통해 불러왔습니다.

생각해보니 and2.tcl파일을 gate2.tcl파일로 바꿔서 매칭되게 하면 더 좋았을것 같네요 앞으로는 그렇게 해야겠어요

다음 source + 주소를 작성하여 simulation을 돌려보겠습니다.

나중에 글 쓰면서 확인해보니 꼭 source 치기 전에 simulation을 미리 눌러서 열어놔야합니다. 안그러면 에러가 뜨더라구여

tcl파일을 이렇게 적어줍니다.

restart

add_force a {0 0ns} {1 50ns} -repeat_every 100ns

add_force b {0 0ns} {1 25ns} -repeat_every 50ns

run 200 ns

Simulation이 열린것을 확인할 수 있습니다.

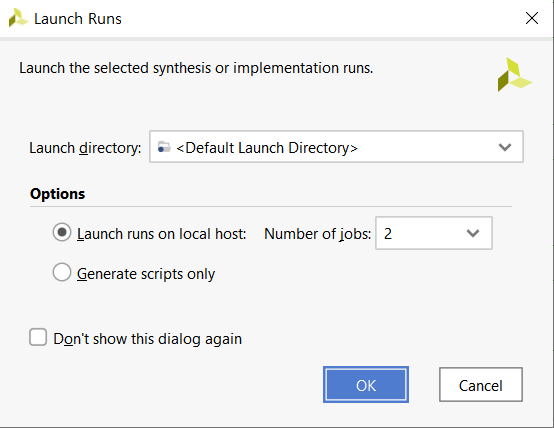

Run Synthesis를 해보겠습니다.

number of jobs 의 숫자가 커질수록 더 좋은 결과를 얻을 수 있습니다.

왜냐하면 결과를 얻기위한 반복할 job의 수 라는 이야기 입니다.

그 결과 delay를 최소화 하거나 사이즈를 최소화할 수 있습니다.

Synthesis의 Schematic을 해보겠습니다.

gate2.v는 Synthesis의 Shematic을 확인하는 것으로 마치겠습니다.~

회로도를 보는방법이 RTL은 코드로부터 로직function으로 우리가알고있는 게이트레벨로 보여주는 방식이고,

Synthesis 는 그 function을 타겟팅하고 있는 반도체에 최종라이브러리로 변환하는 작업이 Synthesis라고 합니다.

이 Synthesis가 xilinx의 라이브러리로 구현이됩니다.

이 부분은 추가적인 설명을 덧붙여서 정리 예정입니다.